# Universidade Federal de Juiz de Fora Curso de Graduação em Engenharia Elétrica Habilitação em Sistemas Eletrônicos

Patrick Protazio Domingues

# CHIP DIDÁTICO PARA ESTUDO DOS BLOCOS CONSTRUTIVOS ANALÓGICOS CMOS

Monografia de Conclusão de Curso

Juiz de Fora 2016 Patrick Protazio Domingues

Chip Didático para Estudo dos Blocos Construtivos Analógicos CMOS

Monografia apresentada a Coordenação do Curso de Engenharia Elétrica da Universidade Federal de Juiz de Fora, Habilitação em Sistemas Eletrônicos, como requisito para aprovação na disciplina CEL046 - Trabalho Final de Curso.

Orientador: Prof. Dr. Estêvão Coelho Teixeira

Juiz de Fora

2016

Ficha catalográfica elaborada através do programa de geração automática da Biblioteca Universitária da UFJF, com os dados fornecidos pelo(a) autor(a)

Domingues, Patrick Protazio.

Chip Didático para Estudo dos Blocos Construtivos Analógicos CMOS / Patrick Protazio Domingues. -- 2016.

61 p.: il.

Orientador: Estêvão Coelho Teixeira Trabalho de Conclusão de Curso (graduação) - Universidade Federal de Juiz de Fora, Faculdade de Engenharia, 2016.

1. Circuitos Integrados. 2. MOSFET. 3. Blocos Analógicos. I. Teixeira, Estêvão Coelho , orient. II. Título.

## Patrick Protazio Domingues

Chip Didático para Estudo dos Blocos Construtivos Analógicos CMOS

Monografia apresentada a Coordenação do Curso de Engenharia Elétrica da Universidade Federal de Juiz de Fora, Habilitação Sistemas Eletrônicos, como requisito para aprovação na disciplina CEL046 - Trabalho Final de Curso.

Aprovada em 09 de Dezembro de 2016.

#### BANCA EXAMINADORA:

Prof. Dr. Estêvão Coelho Teixeira

Universidade Federal de Juiz de Fora, UFJF

Prof. Dr. Fabrício Pablo Virgínio de Campos

Universidade Federal de Juiz de Fora, UFJF

Prof. Dr. Michel Bortolini Hell

Universidade Federal de Juiz de Fora, UFJF

Dedico este trabalho à minha família e a todas as pessoas que me ajudaram desde a matrícula até o momento presente.

## **AGRADECIMENTOS**

Ao Professor Dr. Estêvão Coelho Teixeira pela orientação, ensinamentos, amizade, atenção e paciência durante todo o desenvolvimento deste trabalho.

À PROPESQ, à Universidade Federal de Juiz de Fora e à Faculdade de Engenharia pelo suporte financeiro e por prover as ferramentas necessárias para o desenvolvimento deste trabalho.

"Ou não."

Nimb

**RESUMO**

Este trabalho descreve o design de um chip concebido para melhorar o entendimento

de blocos analógicos CMOS básicos. Ferramentas livres foram usadas na captura

de esquemáticos, simulação, edição de layout, extração e verificação. O chip contém

diferentes tipos de espelhos de corrente, somadores de corrente, chaves analógicas,

pares diferenciais e amplificadores básicos, que são brevemente descritos. Layouts são

mostrados, assim como resultados das simulações.

Palavras Chave: chip; blocos analógicos; ferramentas livres; CMOS;

**ABSTRACT**

This work describes the design of a didactic chip conceived in order to improve

the understanding of the basic analog CMOS building blocks. Free tools were used for

schematics capture, simulation, layout editing, extraction and verification. The chip

contains different types of current mirrors, current adders, analog switches, differential

pairs and basic amplifiers, which are briefly described. Some layouts are shown, as well

as simulation results.

Keywords: chip; analog blocks; free tools; CMOS.

## LISTA DE FIGURAS

| Figura 1  | Interface básica do Linear Technologies LTspice IV                                                                                                                     | 20  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figura 2  | Interface básica do Electric VLSI                                                                                                                                      | 22  |

| Figura 3  | Exemplo da multiplexação dos espelhos nos pinos do chip; $I_{REF}$ é a corrente de referência, $I_{out1}$ é a corrente de saída 1 e $I_{out2}$ é a corrente de saída 2 | 24  |

| D: 4      |                                                                                                                                                                        |     |

| Figura 4  | Desenho esquemático de um espelho simples                                                                                                                              | 27  |

| Figura 5  | Resultado da simulação das correntes de saída de um espelho simples; $I_1$ é a corrente de referência, $I_{R1}$ é a corrente de saída 1, $I_{R2}$ é a corrente         |     |

|           | de saída 2 e $V_{out}$ é a tensão de $V_{DS}$                                                                                                                          | 28  |

| Figura 6  | Layout de um espelho simples descasado de 40uA                                                                                                                         | 28  |

| Figura 7  | Layout de um espelho simples casado de 40uA                                                                                                                            | 29  |

| Figura 8  | Desenho esquemático de um espelho cascode                                                                                                                              | 30  |

| Figura 9  | Resultado da simulação de um espelho cascode de 40uA; $I_1$ é a corrente                                                                                               |     |

|           | de referência, $I_{R1}$ é a corrente de saída 1, $I_{R2}$ é a corrente de saída 2 e                                                                                    | 0.1 |

|           | $V_{n001}$ é a tensão de $V_{DS}$                                                                                                                                      |     |

| Figura 10 | Layout de um espelho cascode de 40uA                                                                                                                                   | 31  |

| Figura 11 | Desenho esquemático de um espelho Wilson                                                                                                                               | 32  |

| Figura 12 | Resultado da simulação de um espelho Wilson de 40uA; $I_1$ é a corrente de referência, $I_{R1}$ é a corrente de saída 1, $I_{R2}$ é a corrente de saída 2 e            |     |

|           | $V_{n001}$ é a tensão de $V_{DS}$                                                                                                                                      | 33  |

| Figura 13 | Layout de um espelho Wilson de 40uA                                                                                                                                    | 33  |

| Figura 14 | Desenho esquemático de um espelho Wilson modificado                                                                                                                    | 34  |

| Figura 15 | Resultado da simulação de um espelho Wilson modificado de 40uA; $I_1$ é a corrente de referência, $I_{R1}$ é a corrente de saída 1, $I_{R2}$ é a corrente de           |     |

|           | saída 2 e $V_{n001}$ é a tensão de $V_{DS}$                                                                                                                            | 35  |

| Figura 16 | Layout de um espelho Wilson modificado de 40u<br>A                                                                                                                     | 35  |

| Figura 17 | Esquemático de um espelho High Compliance                                                                                                                              | 36  |

| Figura 18 | Resultado da simulação de um espelho $High\ Compliance$ de 40uA; $I_1$ é             |    |

|-----------|--------------------------------------------------------------------------------------|----|

|           | a corrente de referência, $I_{R1}$ é a corrente de saída 1, $I_{R2}$ é a corrente de |    |

|           | saída 2 e $V_{n001}$ é a tensão de $V_{DS}$                                          | 37 |

| Figura 19 | Layout de um espelho High Compliance de 40uA                                         | 38 |

| Figura 20 | Desenho esquemático do decodificador 4x16                                            | 39 |

| Figura 21 | Resultado da simulação das saídas de tensão normais do Decodificador                 | 40 |

| Figura 22 | Resultado da simulação das saídas de tensão invertidas do Decodificador              | 40 |

| Figura 23 | Layout de uma das 16 partes do decodificador                                         | 41 |

| Figura 24 | Layout do Decodificador                                                              | 42 |

| Figura 25 | Layout de um somador de correntes nominais de 40uA (in)/80uA (out)                   | 43 |

| Figura 26 | Layout dos blocos básicos analógicos                                                 | 44 |

| Figura 27 | Esquemático de um inversor com carga ativa                                           | 45 |

| Figura 28 | Layout de um inversor com carga ativa                                                | 45 |

| Figura 29 | Esquemático de um seguidor de fonte                                                  | 46 |

| Figura 30 | Layout de um inversor com seguidor de fonte                                          | 47 |

| Figura 31 | Layout apenas do seguidor de fonte                                                   | 47 |

| Figura 32 | Esquemático de um par diferencial                                                    | 48 |

| Figura 33 | Layout dos pares diferenciais                                                        | 48 |

| Figura 34 | Esquema do funcionamento de uma chave ideal                                          | 49 |

| Figura 35 | Esquemático de uma chave CMOS                                                        | 49 |

| Figura 36 | Layout de uma chave CMOS                                                             | 50 |

| Figura 37 | Layout completo da disposição interna do chip.                                       | 51 |

|           |                                                                                      |    |

## LISTA DE TABELAS

| Tabela 1  | Espelhos de corrente NMOS     | 56 |

|-----------|-------------------------------|----|

| Tabela 2  | Espelhos de corrente PMOS     | 57 |

| Tabela 3  | Somadores de corrente         | 57 |

| Tabela 4  | Referências de tensão         | 58 |

| Tabela 5  | Blocos básicos                | 58 |

| Tabela 6  | Chaves analógicas             | 58 |

| Tabela 7  | Transistores independentes    | 59 |

| Tabela 8  | Decodificador                 | 59 |

| Tabela 9  | Alimentação                   | 59 |

| Tabela 10 | Tamanho dos transistores NMOS | 60 |

| Tabela 11 | Tamanho dos transistores PMOS | 61 |

## LISTA DE ABREVIATURAS E SIGLAS

CA - Corrente Alternada

CC - Corrente Contínua

CI - Circuito Integrado

CMOS - Complementary Metal Oxide Semiconductor

CMOS C5 - Tecnologia CMOS com canal de 0.5um

COBENGE - Congresso Brasileiro de Ensino em Engenharia

DIP - Dual In Parallel

DRC - Desing Rules Check

IC - Integrated Circuit

LABEL - Laboratório de Eletrônica

LVS - Layout vs Schematic

MEP - Mosis Educational Program

MOSFET - Metal Oxide Semiconductor Field Effect Transistor

NMOS - nFET Metal Oxide Silicon

PLCC - Plastic Leaded Chip Carrier

PMOS - pFET Metal Oxide Silicon

PROPESQ - Pró-Reitoria de Pós-Graduação e Pesquisa

SBMICRO - Sociedade Brasileira de Microeletrônica

SPICE - Simulation Program with Integrated Circuit Emphasis

UFJF - Universidade Federal de Juiz de Fora

VLSI - Very Large Scale Integration

# LISTA DE SÍMBOLOS

## Unidades

| Comprimento                           |

|---------------------------------------|

| Constante de material do transistor N |

| Constante de material do transistor P |

| Corrente de entrada                   |

| Corrente de referência                |

| Corrente de saída                     |

| Corrente nominal                      |

| Largura                               |

| Resistência                           |

| Tensão                                |

| Tensão de polarização                 |

| Tensão de alimentação                 |

| Tensão entre dreno e fonte            |

| Tensão entre porta e fonte            |

| Tamanho mínimo de medida              |

|                                       |

# SUMÁRIO

| 1    | Introdução                                     | 17 |

|------|------------------------------------------------|----|

| 1.1  | Identificação do Problema                      | 17 |

| 1.2  | Motivação                                      | 17 |

| 1.3  | Objetivos                                      | 17 |

| 1.4  | Estrutura da dissertação                       | 18 |

| 2    | Escolha dos softwares                          | 19 |

| 2.1  | Software para Esquemáticos                     | 19 |

| 2.2  | As regras do Mosis Educational Program         | 20 |

| 2.2. | .1 O Research Program                          | 20 |

| 2.2. | .2 As mudanças na regra                        | 21 |

| 2.3  | Software para Layouts                          | 21 |

| 3    | Definição dos blocos internos                  | 23 |

| 3.1  | O processo de criação de um circuito integrado | 24 |

| 4    | Desenvolvimento dos blocos internos            | 26 |

| 4.1  | Espelhos de Corrente                           | 26 |

| 4.1. | .1 Espelhos simples                            | 27 |

| 4.1. | .2 Espelhos de topologia Cascode               | 30 |

| 4.1. | .3 Espelhos de topologia Wilson                | 32 |

| 4.1. | .4 Espelhos de topologia Wilson modificado     | 34 |

| 4.1. | 5 Espelhos de topologia <i>High Compliance</i> | 36 |

| 4.2  | Decodificador                                  | 39 |

| 4.3                  | Somador de corrente baseado em espelhos cascode                           | 43        |

|----------------------|---------------------------------------------------------------------------|-----------|

| 4.4                  | Blocos analógicos básicos                                                 | 44        |

| 4.4.1                | Amplificador Inversor com carga ativa NMOS                                | 45        |

| 4.4.2                | 2 Seguidor de fonte e amplificador com seguidor de fonte                  | 46        |

| 4.4.3                | B Pares diferenciais                                                      | 48        |

| 4.5                  | Chaves analógicas                                                         | 49        |

| 5 I                  | $Layout 	ext{ final}$                                                     | 51        |

| 6 (                  | Conclusões finais                                                         | <b>52</b> |

| 6.1                  | Conclusões                                                                | 52        |

| 6.2                  | Trabalhos Futuros                                                         | 53        |

| $\operatorname{Ref}$ | erências                                                                  | 54        |

| Αpέ                  | èndice A - Pinagem do chip UFJF                                           | 56        |

| A.1                  | Espelhos de corrente NMOS (Uso total: 4 pinos)                            | 56        |

| A.2                  | Espelhos de corrente PMOS(Uso total: 4 pinos)                             | 57        |

| A.3                  | Somadores de corrente baseados em espelhos cascode (Uso total: 3 pinos) . | 57        |

| A.4                  | Referências de tensão(Uso total: 0 pino)                                  | 58        |

| A.5                  | Blocos Básicos(Uso total: 25 pinos)                                       | 58        |

| A.6                  | Chaves analógicas(Uso total: 3 pinos)                                     | 58        |

| A.7                  | Transistores independentes (Uso total: 0 pino)                            | 59        |

| A.8                  | Decodificador (Uso total: 5 pinos)                                        | 59        |

| A.9                  | Alimentação em geral (Uso total: 4 pinos)                                 | 59        |

| Apé                  | èndice B - Cálculo do tamanho dos transistores                            | 60        |

## 1 INTRODUÇÃO

## 1.1 IDENTIFICAÇÃO DO PROBLEMA

Atualmente, práticas didáticas em laboratório sobre MOSFETs são realizadas utilizando dispositivos discretos, não correspondendo, muitas vezes, à realidade presente em circuitos integrados (CIs) analógicos, por diversos motivos, como o descasamento de componentes. Certos blocos fundamentais, como os espelhos de corrente, dependem que os MOSFETs envolvidos tenham características físicas iguais ou muito próximas, o que, mediante técnicas adequadas, pode ser conseguido em circuitos integrados, mas com grande dificuldade utilizando componentes discretos de CIs comerciais (SEDRA; SMITH, 2007).

## 1.2 MOTIVAÇÃO

As atividades relacionadas à Microeletrônica vêm recebendo crescentes incentivos privados para seu desenvolvimento no País. Tais medidas visam superar uma defasagem nesta área em relação aos países desenvolvidos e mesmo em relação a outros países em desenvolvimento. É importante ressaltar que a indústria de semicondutores fabrica produtos de elevado valor agregado, não devendo ser negligenciada pelos setores governamental e acadêmico.

Sendo assim, viu-se a clara possibilidade de desenvolvimento de um dispositivo integrado ao qual pudesse ser inserido os principais blocos analógicos de estudo no Laboratório de Eletrônica da Faculdade de Engenharia da Universidade Federal de Juiz de Fora.

#### 1.3 OBJETIVOS

Este trabalho tem como objetivo descrever o projeto de um chip com blocos analógicos internos feitos a partir de MOSFETs para estudo no laboratório acima citado,

tanto do processo de construção quanto dos ensaios a partir do protótipo posteriormente.

O trabalho aqui apresentado tem algumas características semelhantes com pesquisas relatadas na literatura, como em BRITO JÚNIOR e SOUSA (2008) e BRITO JÚNIOR e Sousa (2009). Porém apresenta outras bastante inovadoras, em relação ao que já foi produzido. Um ponto que diferencia este trabalho dos outros correlatos é o projeto específico para avaliação de blocos básicos, podendo permitir inclusive a interligação dos mesmos.

O chip, que foi idealizado utilizando-se a tecnologia CMOS C5 (comprimento de canal mínimo 0,5um, 3 camadas de metal e 2 de polisilício) contará com espelhos de corrente, amplificadores, pares diferenciais, etc. Todos os blocos estão listados no Apêndice A. Os blocos montados e simulados podem ser encontrados no Capítulo 4.

## 1.4 ESTRUTURA DA DISSERTAÇÃO

No capítulo 2 serão abordadas as escolhas de *software*, assim como as regras do *Mosis Educational Program*. O processo de definição dos blocos internos e uma lista de passos para criação de um circuito integrado são explicados no capítulo 3. Já no capítulo 4, os desenhos e resultados obtidos são apresentados e analisados. O *layout* final é indicado no capítulo 5 e explicado conforme a distribuição dos blocos. A leitura do capítulo 6 conclui o trabalho, apresentando uma visão geral do projeto e mudanças conforme as novas regras do MEP.

#### 2 ESCOLHA DOS SOFTWARES

A escolha de softwares capazes de reproduzir bem um processo de design de um circuito integrado assim como a capacidade de realizar simulações próximas à realidade foi um passo fundamental pra atual conjuntura deste trabalho. Foi-se necessário considerar dois pontos: a robustez dos programas e os recursos necessários para utilizá-los, chegando-se a conclusão que era de suma importância um uso não vinculado a licenças, optando-se pela gratuidade e possibilidade de implementação dos métodos em sala de aula (DOMINGUES; ALMEIDA; TEIXEIRA, 2016b).

## 2.1 SOFTWARE PARA ESQUEMÁTICOS

A escolha para um programa que fosse capaz de fazer os diagramas esquemáticos necessários para a criação e simulação dos principais blocos foi feita tendo-se como base a capacidade em utilizar-se da precisão necessária para a apresentação de resultados condizente a quantidade de níveis adicionada aos componentes MOSFETs dos blocos.

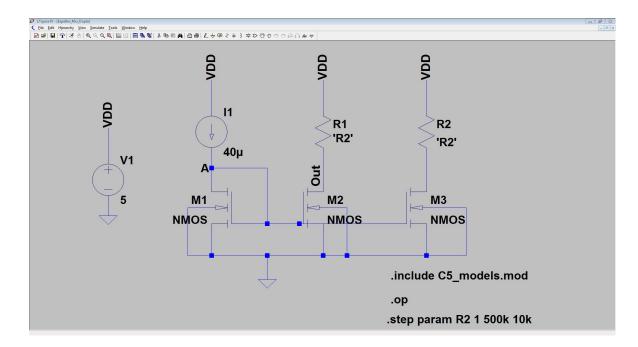

Atendendo aos requisitos já apresentados, os esquemáticos foram feitos no programa de licença livre *Linear Technologies LTspice IV* devido à facilidade de edição e simulação que o programa apresenta, além do seu tamanho reduzido se comparado a outras plataformas SPICE. Na figura 1, pode-se ver a interface básica do *Linear Technologies LTspice IV*.

Os desenhos esquemáticos foram feitos utilizando-se o modelo do arquivo C5\_models.mod. Este modelo é disponibilizado publicamente em Baker (2015) e se aproxima dos modelos SPICE comerciais para a tecnologia C5 (os quais são obtidos mediante declaração de não-divulgação por parte dos projetistas).

Figura 1: Interface básica do Linear Technologies LTspice IV

#### 2.2 AS REGRAS DO MOSIS EDUCATIONAL PROGRAM

Em uma tentativa de ajudar as instituições educacionais no desenvolvimento de programas de instrução e pesquisa em circuitos integrados dentro de seus departamentos de engenharia, o MOSIS iniciou o MOSIS Educational Program (MEP). O MEP incluiu um componente instrucional para suporte de classes em VLSI design para dar aos alunos a oportunidade de experimentar o ciclo completo do desenho VLSI, fabricação e testes de um circuito integrado, e um componente da pesquisa para suportar a pesquisa sem investimentos conduzida por estudantes graduados e pela faculdade que necessitam desenvolver a massa crítica em suas áreas de pesquisa a fim de atrair o financiamento para a pesquisa futura. Ambos os componentes do MEP são oferecidos sem custo para as universidades, com restrições mínimas baseadas em tecnologias MOSIS suportadas e programação de fabricação.

#### 2.2.1 O RESEARCH PROGRAM

O programa de pesquisa do MOSIS oferece uma oportunidade para pesquisadores afiliados a uma universidade para fabricar um projeto que de outra forma não seria fabricado.

O MOSIS subsidia os custos de fabricação de um chip por universidade (ou por campus universitário, no caso de universidades estaduais com vários campi) por ano,

com uma área de chip não superior a 4 milímetros quadrados.

Esta fabricação de chips gratuitos exige uma proposta de pesquisa MEP juntamente com uma carta certificando que o trabalho de pesquisa não é financiado. A fabricação deste chip livre é fornecida numa base de "espaço disponível" o que significa que o MOSIS não pode garantir a fabricação no calendário selecionado pelo requerente. O custo de encapsulamento é separado e não incluído para os projetos do MEP.

## 2.2.2 AS MUDANÇAS NA REGRA

As regras descritas acima são as vigentes atualmente, mas o trabalho aqui descrito foi construído antes das mudanças:

Antes era fabricado um lote com 40 circuitos integrados não encapsulados, cabendo ao requerente solicitar um tipo de encapsulamento desejado e pagar os custos do mesmo. Além disso, a área máxima permitida era de  $5,76 \ mm^2$ . Atualmente, o lote é de 5 chips encapsulados até 40 pinos (DIP40) e área máxima de  $4mm^2$ .

#### 2.3 SOFTWARE PARA LAYOUTS

Inicialmente, pensou-se em usar para a construção dos *layouts*, tanto dos blocos individuais quanto do chip por completo, o *Mentor Graphics IC Nanometer Design* que é uma aplicação paga e desenvolvida para a plataforma *Linux*, porém viu-se a possibilidade de dificuldades na posterior renovação da licença anual do pacote, inviabilizando sua utilização. Decidiu-se então pelo desenvolvimento de *layouts* em um programa preferencialmente gratuito.

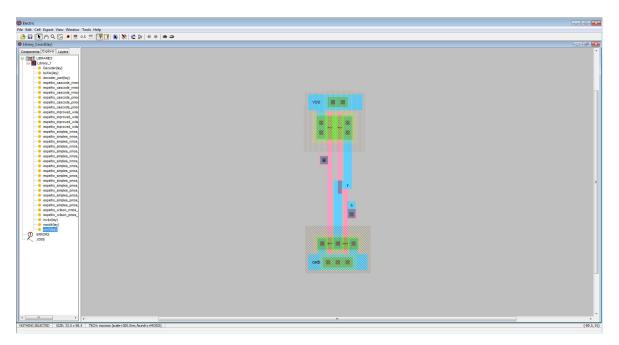

Após certa pesquisa, viu-se a viabilidade da utilização do simples e versátil aplicativo Electric VLSI, totalmente desenvolvido em JAVA e com licença livre para modificações ainda, oferecia também um desafio: desenvolver completamente um chip utilizando somente programas gratuitos.

Ele utiliza regras escaláveis de edição de layout, onde é atribuído um valor  $\lambda = 300$ nm e a partir da base de regras para design do MOSIS (serviço multiusuário que faz a interface entre centros de pesquisa e fabricantes de circuitos integrados (foundries)) faz a revisão de distâncias mínimas, entre outros problemas que podem existir em um layout. Esse conjunto de regras é conhecido como SCMOS. (THE MOSIS SERVICE, 2015)

A vantagem das regras de projeto SCMOS é que elas são públicas e aplicáveis a diferentes processos de fabricação, ao contrário das regras próprias dos fabricantes que são de acesso restrito. Além disso, o programa é capaz de gerar uma netlist pra simulação e comparação com o esquemático. Já as desvantagens ficam por conta da falta de assistência e demora na correção de bugs.

O manual de uso do programa *Electric* está disponível em STATIC FREE SOFTWARE (2015a), uma das páginas do site próprio STATIC FREE SOFTWARE (2015b) contendo em seus domínios vários outros projetos e bibliotecas. Além disso, o site Baker (2015), possui vários tutoriais e materiais para quem deseja trabalhar com *layout* de MOSFETs, além de um grupo de discussão sobre o aplicativo em GOOGLE GROUPS (2015). Ainda, é possível encontrar na literatura exemplos de chips reais fabricados utilizando esta plataforma, como em Montierth, Yap e Baker (2009) e Roy e Baker (2014). Na figura 2, pode-se ver a interface básica do *Electric*.

Figura 2: Interface básica do Electric VLSI

## 3 DEFINIÇÃO DOS BLOCOS INTERNOS

A definição dos blocos internos passou por vários processos de eliminação e escolhas. Primeiramente, deveria ser definido o que é possível ser feito, em seguida, define-se a viabilidade dado o tempo que é necessário e de acordo com os pinos disponíveis para um posterior encapsulamento.

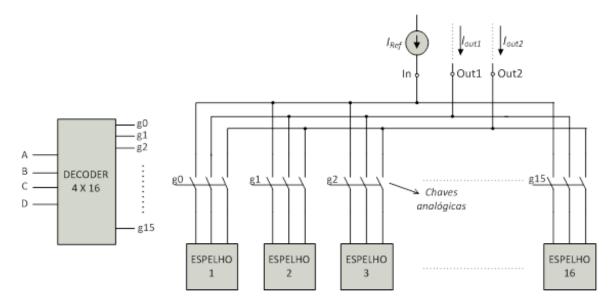

Definiu-se primeiro os espelhos de corrente que seriam inseridos no chip, porém, somente eles, já seriam capazes de ocupar grande parte dos pinos disponíveis até nos maiores encapsulamentos do mercado. Decidiu-se então inserir um decodificador 4x16 (4 entradas, 16 saídas), que permite multiplexar 3 pinos para serem usados em 16 espelhos de corrente diferentes (entrada, saída 1 e saída 2), através de chaves analógicas CMOS. O diagrama que representa essa topologia é apresentado na Figura 3. Tal estrutura foi implementada tanto para os espelhos NMOS como para os PMOS e não foi encontrada na literatura, em trabalhos semelhantes sobre chips didáticos.

Um espelho de corrente é um circuito projetado para copiar a corrente elétrica que passa em um dispositivo ativo por meio do controle da corrente em outro dispositivo ativo de um circuito, mantendo a corrente de saída constante, independentemente da carga, idealmente. A corrente sendo copiada pode ser tanto CC pura (caso comum nos circuitos de polarização), como pode eventualmente conter uma componente CA (neste caso, aplica-se os espelhos em circuitos de processamento de sinais).

Conceitualmente, um espelho de corrente ideal é simplesmente um amplificador ideal e é usado para fornecer correntes de polarização e cargas ativas a circuitos. Os espelhos do chip em questão foram projetados utilizando pares casados e descasados de transistores, contendo uma entrada de referência para a corrente e duas saídas com as correntes "copiadas".

Não é convencional utilizar-se de duas saídas nesses casos, porém isto foi pensado por duas razões básicas: comparar o valor da corrente de saída em relação à entrada e comparar os valores de duas correntes de saída para uma mesma entrada. Neste caso,

espera-se que, para espelhos casados, a diferença entre as duas correntes seja desprezível. Por motivos de teste, pares descasados também foram projetados, para se comparar eventuais diferenças entre estas correntes na prática, já que a dificuldade em simular descasamentos em circuitos integrados foge do escopo deste trabalho.

Em seguida, decidiu-se que usar o maior encapsulamento (68 pinos) poderia ser inviável, tanto por tempo disponível para a conclusão do projeto quanto financeiramente. Optou-se então pela redução da quantidade de blocos disponíveis para que fosse utilizado um encapsulamento PLCC de 52 pinos. Os blocos que foram cortados do projeto são também apresentados no Apêndice A. Na figura 3 abaixo, pode-se ver um exemplo da multiplexação dos espelhos nos pinos do chip.

Figura 3: Exemplo da multiplexação dos espelhos nos pinos do chip;  $I_{REF}$  é a corrente de referência,  $I_{out1}$  é a corrente de saída 1 e  $I_{out2}$  é a corrente de saída 2

## 3.1 O PROCESSO DE CRIAÇÃO DE UM CIRCUITO INTEGRADO

O processo inteiro de fabricação consiste em várias etapas, da idealização do projeto aos testes finais, passando pelos seguintes passos:

- 1. Idealização do Projeto

- 2. Escolha da tecnologia a ser utilizada

- 3. Escolha dos softwares

- 4. Desenho dos esquemáticos

- 5. Simulação dos esquemáticos

- 6. Edição do layout

- 7. Verificação do layout DRC

- 8. Simulação do layout

- 9. Verificação da compatibilidade entre esquemático e layout LVS

- 10. Envio do projeto

- 11. Fabricação do chip

- 12. Encapsulamento

- 13. Testes Finais

Devido as mudanças nas regras descritas em THE MOSIS SERVICE (2015) e suas devidas rodadas de fabricação através do programa *Educational Program*, os processos de 10 a 13 não foram iniciados, porém o projeto do chip, com os devidos testes (DRC, LVS, simulações), até o processo 9, foi concluído com êxito e é apresentado a seguir.

#### 4 DESENVOLVIMENTO DOS BLOCOS INTERNOS

Este capítulo é reservado à apresentação da criação dos blocos internos do chip. Pela quantidade repetitiva de *layout*s com a mesma estrutura, apenas um de cada modelo será descrito, devendo-se subentender que os outros serão similares, mudando-se apenas as suas relações de tamanhos de largura e comprimento, assim como o material principal de seu poço, ou seja, como nos exemplos mostrados serão usados os MOSFETs do tipo NMOS (que são construídos em poço do tipo P), logo poço do tipo N é pressuposto para construções PMOS. As partes disponíveis estão na lista a seguir e foram desenvolvidas segundo a metodologia de projeto apresentada em Maloberti (2001).

#### 4.1 ESPELHOS DE CORRENTE

Foram desenhados dezesseis espelhos de corrente NMOS e o mesmo número de espelhos PMOS, todos eles possuindo duas saídas cada um. As topologias adotadas foram:

- Simples

- Cascode

- Wilson

- Wilson modificado

- High Compliance

Importante notar que nas simulações, as correntes de saída se manterão próximas às correntes de referência enquanto as tensões entre dreno e fonte dos transistores de saída mantiverem-se próxima à tensão de *overdrive* descrita no Apêndice B.

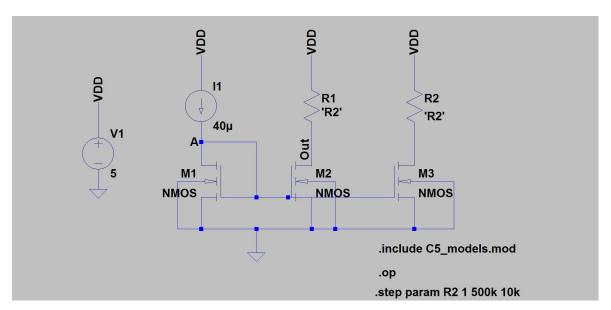

## 4.1.1 ESPELHOS SIMPLES

Os espelhos simples, assim como todos os outros, foram desenhados com duas saídas para podermos estudar como a realimentação dupla pode funcionar nesses espelhos, para também assegurar que, caso alguma das saídas deixe de funcionar, uma ainda estará disponível para uso, além de poder comparar resultados com diferentes resistências de saída.

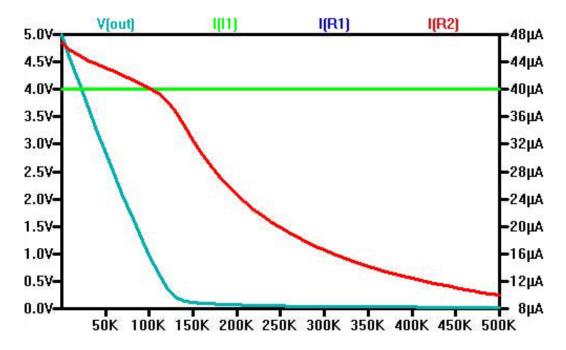

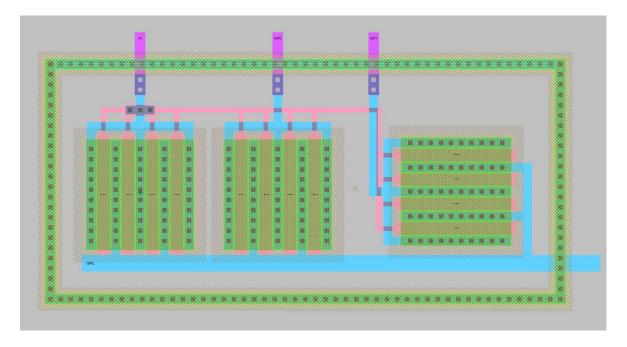

Para o espelho simples NMOS, de entrada nominal de 40uA, foi realizada a simulação do ponto de operação para diferentes valores da resistência de saída, variando de 1  $\Omega$  até 500 k $\Omega$ , em intervalos de 10 k $\Omega$ . As figuras 4, 5, 6 e 7 mostram esquemático, simulação das correntes e tensões de saída a partir da corrente de referência constante e *layout*s do espelho simples.

Figura 4: Desenho esquemático de um espelho simples

Figura 5: Resultado da simulação das correntes de saída de um espelho simples;  $I_1$  é a corrente de referência,  $I_{R1}$  é a corrente de saída 1,  $I_{R2}$  é a corrente de saída 2 e  $V_{out}$  é a tensão de  $V_{DS}$

Figura 6: Layout de um espelho simples descasado de 40uA

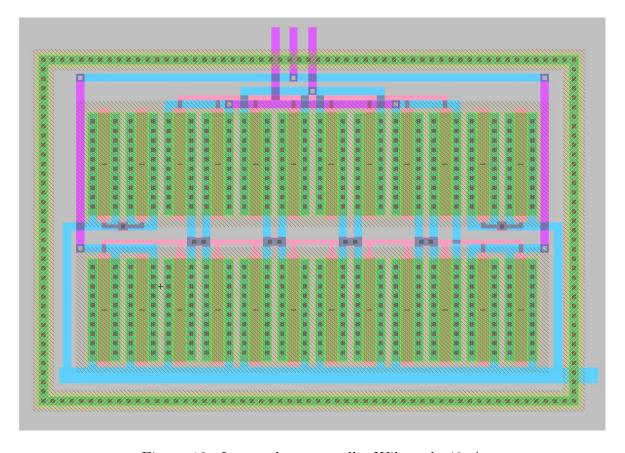

Figura 7: Layout de um espelho simples casado de  $40\mathrm{uA}$

## 4.1.2 ESPELHOS DE TOPOLOGIA CASCODE

Para suprimir o erro introduzido pelo efeito de modulação de comprimento de canal, pode-se utilizar espelhos de correntes cascode. A ideia do uso do espelho de corrente cascode é casar o  $V_{DS}$  dos transistores, M1 e M2. (MALOBERTI, 2001)

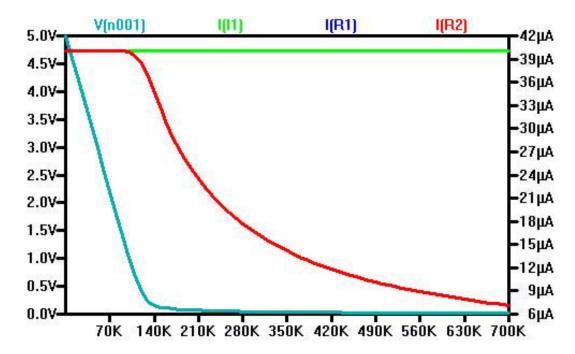

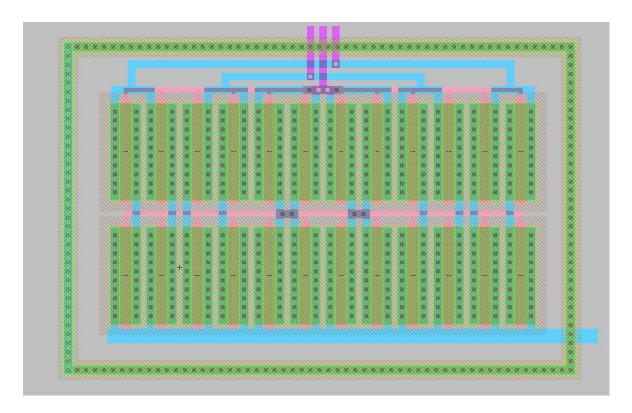

Para o espelho cascode NMOS, de entrada nominal de 40uA, foi realizada a simulação do ponto de operação para diferentes valores da resistência de saída, variando de 1 $\Omega$  até 700 k $\Omega$ , em intervalos de 10 k $\Omega$ , a faixa de operação é maior que o espelho simples devido a correção empregada pela topologia. As figuras 8, 9 e 10 mostram esquemático, simulação das correntes e tensões de saída a partir da corrente de referência constante e layout do espelho cascode.

Figura 8: Desenho esquemático de um espelho cascode

Figura 9: Resultado da simulação de um espelho cascode de 40uA;  $I_1$  é a corrente de referência,  $I_{R1}$  é a corrente de saída 1,  $I_{R2}$  é a corrente de saída 2 e  $V_{n001}$  é a tensão de  $V_{DS}$

Figura 10: Layout de um espelho cascode de 40uA

## 4.1.3 ESPELHOS DE TOPOLOGIA WILSON

Esta topologia é uma configuração para espelhos de corrente desenhada para prover uma fonte de corrente mais constante, além de um ganho de saída sobre a entrada mais preciso. Uma característica notável dessa topologia é o nível de corrente de saída que é ligeiramente menor do que a referência.(MALOBERTI, 2001)

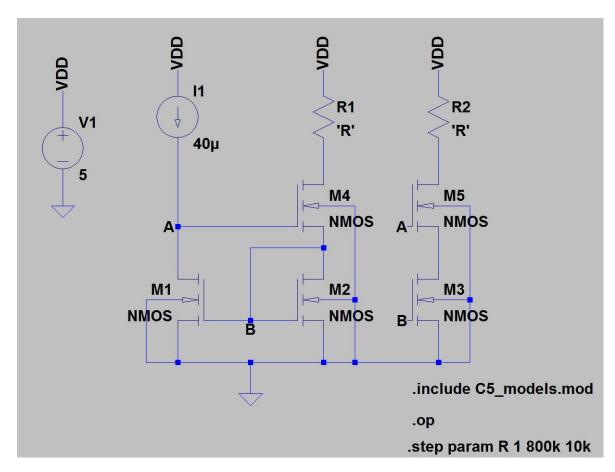

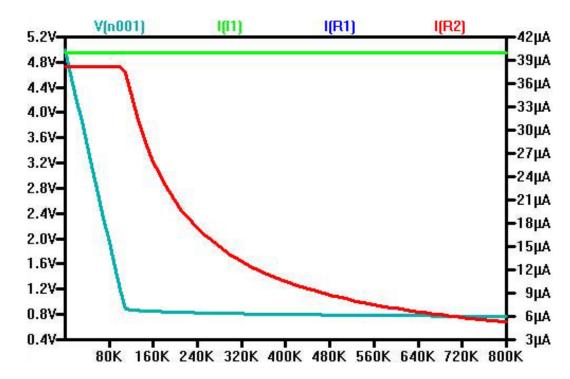

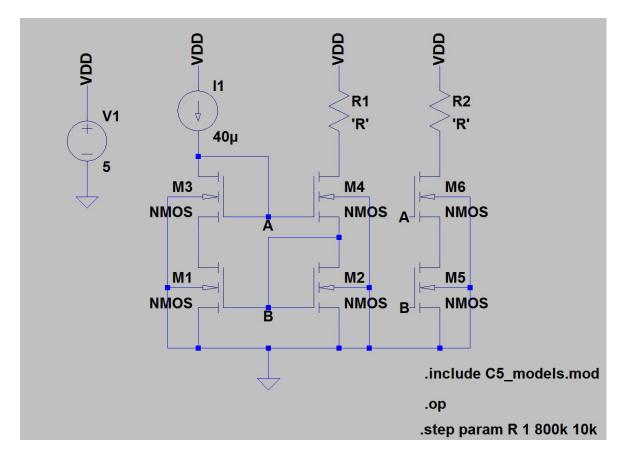

Para o espelho Wilson NMOS, de entrada nominal de 40uA, foi realizada a simulação do ponto de operação para diferentes valores da resistência de saída, variando de 1 $\Omega$  até 800 k $\Omega$ , em intervalos de 10 k $\Omega$ , a faixa de operação é ainda maior que os espelhos já citados devido a correção empregada pela topologia. As figuras 11, 12 e 13 mostram esquemático, simulação das correntes e tensões de saída a partir da corrente de referência constante e layout do espelho Wilson.

Figura 11: Desenho esquemático de um espelho Wilson

Figura 12: Resultado da simulação de um espelho Wilson de 40uA;  $I_1$  é a corrente de referência,  $I_{R1}$  é a corrente de saída 1,  $I_{R2}$  é a corrente de saída 2 e  $V_{n001}$  é a tensão de  $V_{DS}$

Figura 13: Layout de um espelho Wilson de 40uA

## 4.1.4 ESPELHOS DE TOPOLOGIA WILSON MODIFICADO

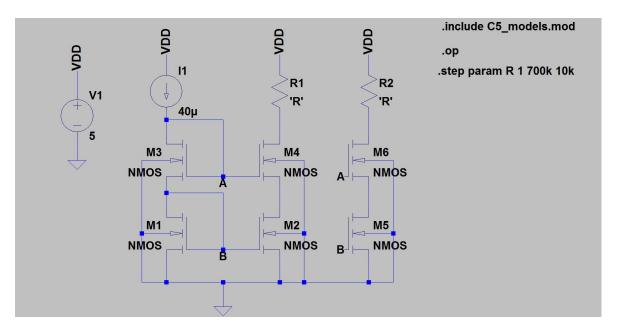

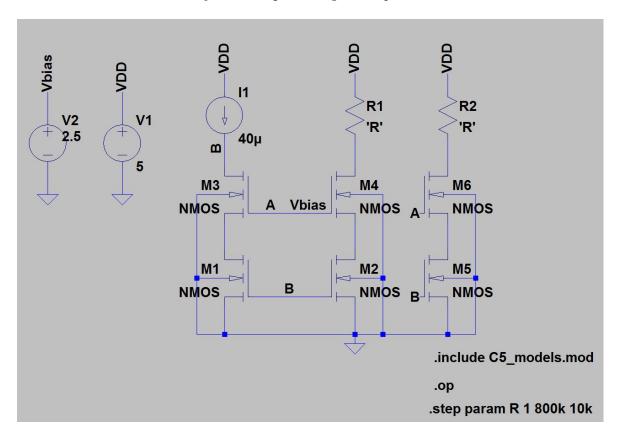

O erro sistemático na corrente do espelho Wilson pode ser compensado por esta solução. Um transistor adicional  $(M_3)$  é usado para abaixar a tensão na porta dos transistores  $M_4$  e  $M_6$ . Com isso, a corrente consegue atingir o valor de referência, apresentando resultado ligeiramente melhor que a configuração cascode. (MALOBERTI, 2001)

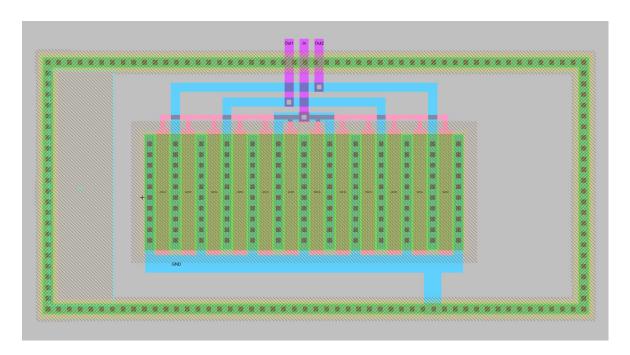

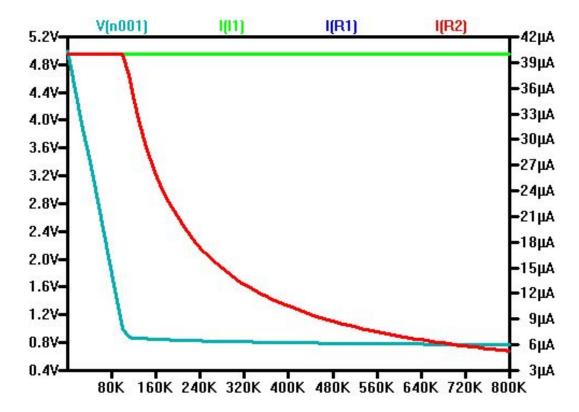

Para o espelho Wilson modificado NMOS, de entrada nominal de 40uA, foi realizada a simulação do ponto de operação para diferentes valores da resistência de saída, variando de 1 $\Omega$  até 800 k $\Omega$ , em intervalos de 10 k $\Omega$ , a faixa de operação é similar ao espelho Wilson. As figuras 14, 15 e 16 mostram esquemático, simulação das correntes e tensões de saída a partir da corrente de referência constante e *layout* do espelho Wilson.

Figura 14: Desenho esquemático de um espelho Wilson modificado

Figura 15: Resultado da simulação de um espelho Wilson modificado de 40uA;  $I_1$  é a corrente de referência,  $I_{R1}$  é a corrente de saída 1,  $I_{R2}$  é a corrente de saída 2 e  $V_{n001}$  é a tensão de  $V_{DS}$

Figura 16: Layout de um espelho Wilson modificado de 40uA

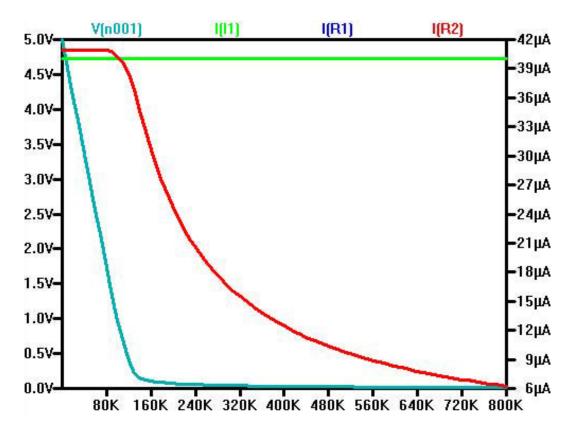

## 4.1.5 ESPELHOS DE TOPOLOGIA HIGH COMPLIANCE

Um espelho  $High\ Compliance$  é usado para evitar um possível descasamento e a complexidade de um circuito Cascode modificado. As tensões  $V_{DS}$  são controladas pela tensão de porta dos transistores que recebe a corrente de referência de  $40\mathrm{uA}$  e o que está em contato direto com a corrente de saída. (MALOBERTI, 2001)

Para o espelho  $High\ Compliance\ NMOS$ , de entrada nominal de 40uA, foi realizada a simulação do ponto de operação para diferentes valores da resistência de saída, variando de  $1\ \Omega$  até  $800\ k\Omega$ , em intervalos de  $10\ k\Omega$  com  $V_{BIAS}=2.5V$ . As figuras 17, 18 e 19 mostram esquemático, simulação das correntes e tensões de saída a partir da corrente de referência constante e layout do espelho  $High\ Compliance$ .

Figura 17: Esquemático de um espelho High Compliance

Figura 18: Resultado da simulação de um espelho  $High\ Compliance$  de 40uA;  $I_1$  é a corrente de referência,  $I_{R1}$  é a corrente de saída 1,  $I_{R2}$  é a corrente de saída 2 e  $V_{n001}$  é a tensão de  $V_{DS}$

Figura 19: Layout de um espelho  ${\it High~Compliance}$  de 40uA

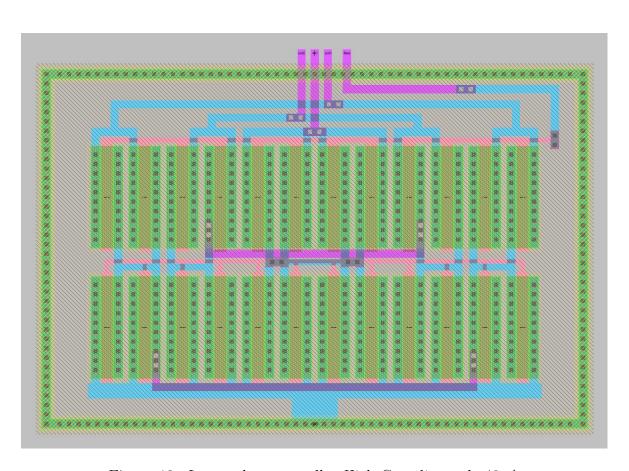

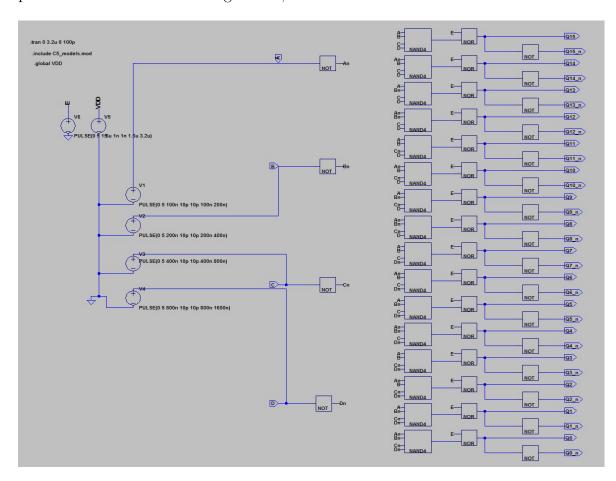

### 4.2 DECODIFICADOR

O decodificador é o único bloco digital de todo o projeto, sendo utilizado para multiplexar os pinos de saída de forma que os 16 espelhos NMOS utilizam 4 pinos e os espelhos PMOS, outros 4 pinos.

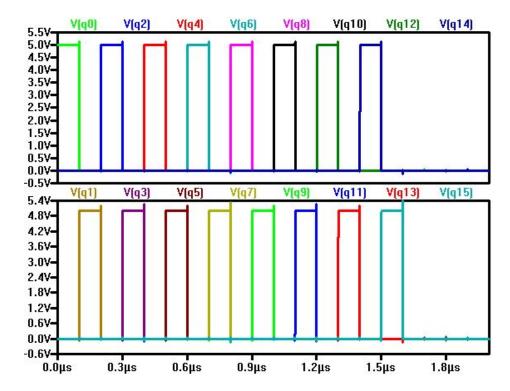

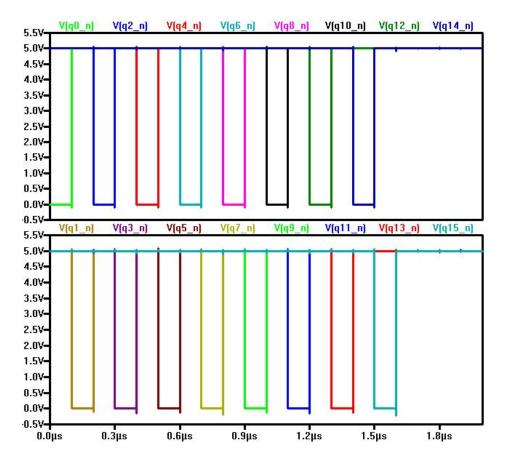

A simulação foi feita de forma que as entradas recebessem todas as combinações de valores possíveis. O esquemático e os resultados da simulação para as tensões de saída podem ser vistos abaixo nas figuras 20, 21 e 22.

Figura 20: Desenho esquemático do decodificador 4x16

Figura 21: Resultado da simulação das saídas de tensão normais do Decodificador

Figura 22: Resultado da simulação das saídas de tensão invertidas do Decodificador

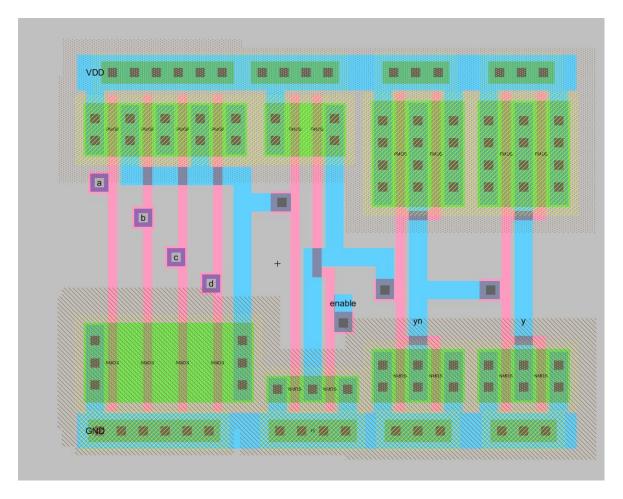

As partes do decodificador são construídas utilizando-se de uma porta NAND4 (NAND de 4 entradas), uma porta NOR para funcionar como um *enable* do decodificador e duas portas inversoras NOT para funcionarem com um *buffer* como pode ser visto na figura 23. A figura do *layout* completo do decodificador é numerada 24.

Figura 23: Layout de uma das 16 partes do decodificador

Figura 24: Layout do Decodificador

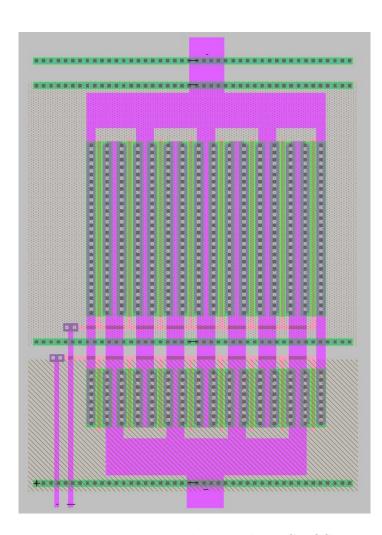

### 4.3 SOMADOR DE CORRENTE BASEADO EM ESPELHOS CASCODE

Dois espelhos cascode são interligados para atuarem como um somador de corrente, o qual possui duas entradas distintas que se somam no interior do bloco para uma corrente maior. No chip em questão, o valor nominal é de 40uA, podendo-se utilizar outros valores aceitáveis para a tecnologia. A figura 25 mostra o *layout* deste bloco.

Figura 25: Layout de um somador de correntes nominais de 40uA (in)/80uA (out)

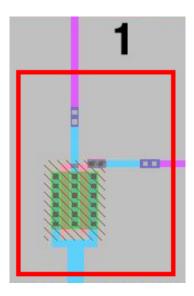

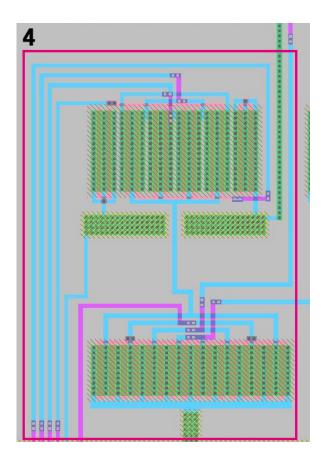

# 4.4 BLOCOS ANALÓGICOS BÁSICOS

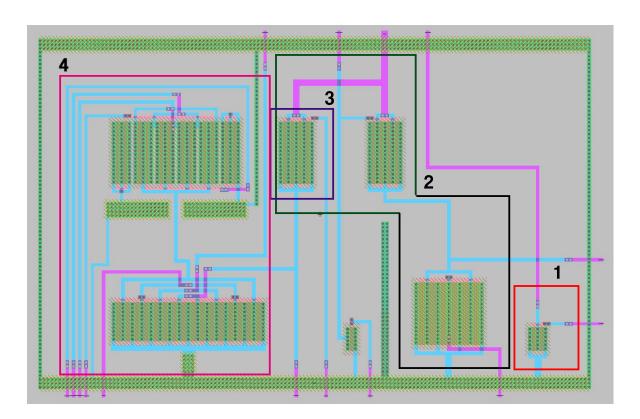

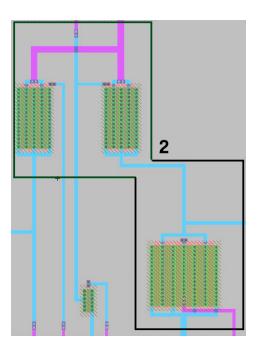

Nesta seção apresentam-se os blocos analógicos básicos contidos no projeto. Cada uma das topologias será descrita a seguir usando-se como referência sua construção NMOS. Na figura 26 pode-se ver o *layout* dos blocos básicos juntos da forma que foram desenhados no *layout* final do chip completo. Os blocos numerados podem ser vistos como:

- 1. Amplificador inversor

- 2. Amplificador inversor com seguidor de fonte

- 3. Seguidor de fonte

- 4. Pares diferenciais

Figura 26: Layout dos blocos básicos analógicos

### 4.4.1 AMPLIFICADOR INVERSOR COM CARGA ATIVA NMOS

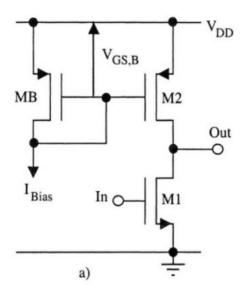

A forma mais simples de estágio de ganho é obtida através da utilização de um inversor com carga ativa. Diferentemente de sua versão digital, o sinal de entrada é aplicado a apenas um transistor, enquanto seu elemento complementar é uma fonte de polarização com uma tensão constante e atua como uma carga ativa. As figuras 27 e 28 mostram esquemático e *layout* do bloco.

Figura 27: Esquemático de um inversor com carga ativa

Figura 28: Layout de um inversor com carga ativa

# 4.4.2 SEGUIDOR DE FONTE E AMPLIFICADOR COM SEGUIDOR DE FONTE

Um inversor com carga ativa produz um ganho de tensão conveniente. Contudo, a impedância de saída é relativamente alta e não é aceitável para ganhos em cargas resistivas pequenas ou cargas capacitivas grandes. Então é necessária a adição de um estágio de saída: o seguidor de fonte, que atua como um bloco básico para alcançar uma baixa impedância de saída ou uma troca de nível de tensão. As figuras 29, 30 e 31 mostram esquemático e *layouts* do bloco.

Figura 29: Esquemático de um seguidor de fonte

Figura 30: Layout de um inversor com seguidor de fonte

Figura 31: Layout apenas do seguidor de fonte

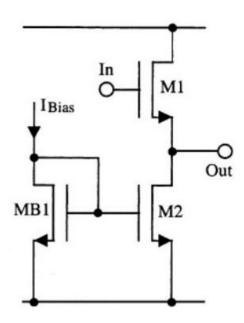

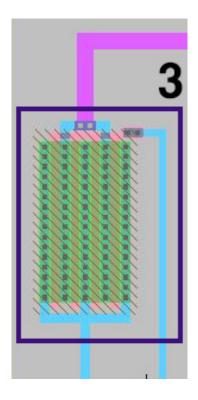

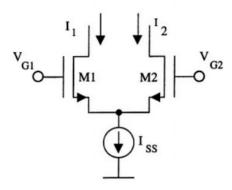

### 4.4.3 PARES DIFERENCIAIS

Os pares diferenciais são largamente utilizados como estágio de entrada, construído de forma que ambos os MOSFETs de entrada tem uma característica de fonte comum, alimentadas por fontes de corrente. As figuras 32 e 33 mostram esquemático e *layout* do bloco.

Figura 32: Esquemático de um par diferencial

Figura 33: Layout dos pares diferenciais

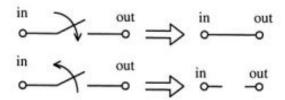

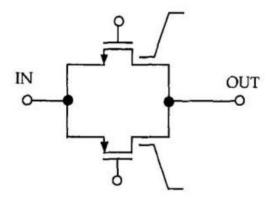

## 4.5 CHAVES ANALÓGICAS

Uma chave ideal é um curto circuito no estágio de 'on' e um circuito aberto no estágio de 'off', usada meramente para transferir uma carga de um nó para outro e definir uma voltagem num ponto de alta impedância. Para este tipo de uso, após um tempo mínimo, a corrente em uma chave vai para zero ou é negligenciável. Essas condições de uso são facilmente implementadas por um transistor do tipo MOS ou um par de transistores complementares. As figuras 34, 35 e 36 mostram esquema de funcionamento, esquemático e *layout* de uma chave com partes NMOS e PMOS.

Figura 34: Esquema do funcionamento de uma chave ideal

Figura 35: Esquemático de uma chave CMOS

Figura 36: Layout de uma chave CMOS

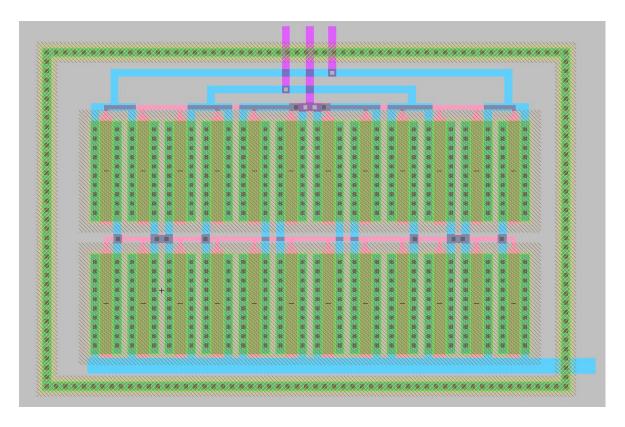

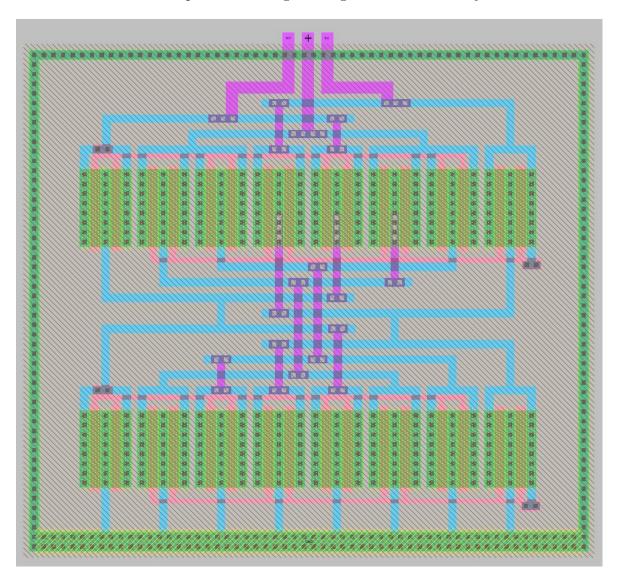

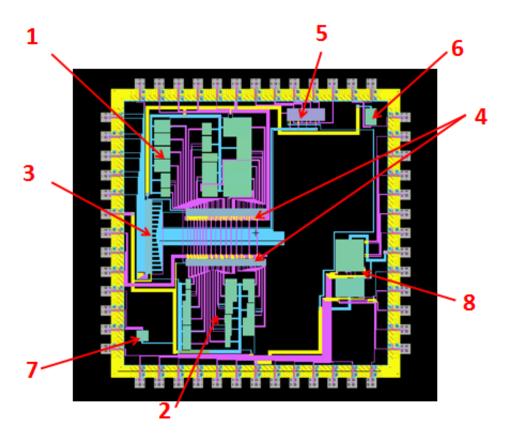

### 5 LAYOUT FINAL

Para ilustrar como será o desenho final do chip por completo, apresenta-se aqui a disposição dos blocos internos anteriormente descritos. Um padframe, já construído e disponibilizado pelo Baker (2015), foi utilizado para ajustar o modelo final para a fabricação, como pode ser visto abaixo na figura 37. Os blocos identificados abaixo são: (1) Espelhos PMOS; (2) Espelhos NMOS; (3) Decodificador 4x16; (4) Chaves analógicas do multiplexador dos espelhos; (5) Chaves analógicas de uso geral; (6) Somador de corrente PMOS; (7) Somador de corrente NMOS; (8) Blocos analógicos básicos (contêm os inversores analógicos, seguidor de fonte e pares diferenciais).

Figura 37: Layout completo da disposição interna do chip.

#### 6 CONCLUSÕES FINAIS

## 6.1 CONCLUSÕES

Este trabalho apresentou o projeto de um chip experimental para estudo dos principais blocos construtivos de circuitos integrados analógicos CMOS. Acredita-se que, após sua fabricação, o chip desenvolvido será de grande utilidade nos cursos tanto de graduação como de pós-graduação em Engenharia Elétrica, para assimilação dos conceitos relativos a dispositivos CMOS, especialmente aplicados à Eletrônica Analógica, imprescindível para etapas comuns no processamento de sinais, como amplificação e conversão analógica-digital.

O material aqui apresentado foi submetido para publicação no Congresso Brasileiro de Educação em Engenharia (COBENGE) e SBMicro 16<sup>th</sup> Conference Chip-on-the-mountains gerando as publicações Domingues, Almeida e Teixeira (2016b) e Domingues, Almeida e Teixeira (2016a), respectivamente. Dois principais motivos favoreceram o aceite do trabalho nestes eventos, com a possibilidade da inclusão em outros:

- O desenvolvimento de um chip para estudo dos blocos analógicos.

- A construção de todas as etapas utilizando-se software livre.

O desafio da execução deste projeto em programas livres e/ou gratuitos é algo pouco difundido, o que tornaram estes resultados ainda mais interessantes. Esta motivação está associada à disseminação da Microeletrônica no meio acadêmico, já que ferramentas comerciais, apesar de possuírem capacidade de desenvolvimento de chips nas novas tecnologias nanométricas, também possuem restrições relativas ao acesso e tempo de aprendizado.

Vale ressaltar que todos os testes de DRC e LVS foram concluídos com sucesso, não cabendo discutir o processo ou resultados no escopo deste trabalho.

### 6.2 TRABALHOS FUTUROS

Para o desenvolvimento e posterior fabricação, conta-se com o apoio do serviço multiusuário MOSIS (www.mosis.com), no qual a Faculdade de Engenharia da UFJF se cadastrou para submissão de um projeto em seu programa de apoio a pesquisas: MEP (MOSIS Educational Program). O MEP permite, para os projetos aprovados, a fabricação de um chip sem custo por ano por instituição e para isso será necessário adequar o projeto às novas regras do programa.

Haverá uma redução no encapsulamento do chip, pois a nova regra permite apenas que seja usado o modelo DIP de 40 pinos tendo área máxima de  $4mm^2$ . Ambos fatores levarão o projeto a uma mudança e consequente redução na quantidade de circuitos internos.

## REFERÊNCIAS

- BAKER, R. J. *Electric VLSI Design System at CMOSedu.com*. 2015. Disponível em: <a href="http://cmosedu.com/cmos1/electric/electric.htm">http://cmosedu.com/cmos1/electric/electric.htm</a>. Acesso em: 10 jan. 2015.

- BRITO JÚNIOR, F. M.; SOUSA, F. R. A didactic chip for use in introductory microelectronics courses. In: *VIII Student Forum on Microelectronics*. [S.l.: s.n.], 2008.

- BRITO JÚNIOR, F. M.; SOUSA, F. R. Measurement results of the ufrn didactic chip. In: *Proceedings of the IX Microelectronics Students Forum.* [S.l.: s.n.], 2009.

- DOMINGUES, P. P.; ALMEIDA, R. V.; TEIXEIRA, E. C. Design of a didactic chip for study of the basic analog cmos building blocks. In: *Sbmicro 2016 Chip on the mountains.* [s.n.], 2016. p. 1–4. Disponível em: <a href="http://www.sbmicro.org.br/images/stories/Eventos/sforum2016/07.pdf">http://www.sbmicro.org.br/images/stories/Eventos/sforum2016/07.pdf</a>>. Acesso em: 11 nov. 2016.

- DOMINGUES, P. P.; ALMEIDA, R. V.; TEIXEIRA, E. C. Uso de software livre em atividades de ensino e pesquisa em microeletrônica. In: *Congresso Brasileiro de educação em engenharia COBENGE*. [s.n.], 2016. p. 1–10. Disponível em: <a href="https://www.researchgate.net/profile/Estevao\_Teixeira/publication/308889309/\_Uso\\_de\\_Software\\_Livre\\_em\\_Atividades\\_de\\_Ensino\\_e\\_Pesquisa\\_em\\_Microeletronica/links/57f4fa8908ae8da3ce5516bf.pdf?origin=publication\\_detail>. Acesso em: 11 nov. 2016.

- GOOGLE GROUPS. *Electric VLSI Editor*. 2015. Disponível em: <a href="https://groups.google.com/forum/\#!forum/electricvlsi">https://groups.google.com/forum/\#!forum/electricvlsi</a>. Acesso em: 01 ago. 2015.

- MALOBERTI, F. Analog Design for CMOS VLSI Systems. 1. ed. [S.l.]: Kluwer Academic Publishers, 2001.

- MONTIERTH, D.; YAP, K.; BAKER, R. J. Cmos image sensor using delta-sigma modulation. In: 4th Annual Austin Conference on Integrated Circuits & Systems. [S.l.: s.n.], 2009.

- ROY, A.; BAKER, R. J. A passive 2nd-order sigma-delta modulator forlow-power analog-to-digital conversion. In: *Proceedings of the IEEE 57th International Midwest Symposium on Circuits and Systems.* [S.l.: s.n.], 2014.

- SEDRA, A.; SMITH, K. Microeletrônica. 5. ed. [S.l.]: Pearson/Prentice Hall, 2007.

- STATIC FREE SOFTWARE. *The Electric User's Manual*. 2015. Disponível em: <a href="http://staticfreesoft.com/jmanual/ElectricManual-9.06.pdf">http://staticfreesoft.com/jmanual/ElectricManual-9.06.pdf</a>>. Acesso em: 10 jan. 2015.

- STATIC FREE SOFTWARE. *Electric VLSI Design System.* 2015. Disponível em: <a href="http://staticfreesoft.com/index.html">http://staticfreesoft.com/index.html</a>>. Acesso em: 10 jan. 2015.

THE MOSIS SERVICE. MOSIS Scalable CMOS (SCMOS). 2015. Disponível em: <a href="https://www.mosis.com/files/scmos/scmos.pdf">https://www.mosis.com/files/scmos/scmos.pdf</a>>. Acesso em: 26 fev. 2016.

# APÊNDICE A - PINAGEM DO CHIP UFJF

O projeto foi feito pensando-se em uma grande quantidade de blocos internos para um encapsulamento máximo de 52 pinos, porém a redução para 40 limitou o projeto de forma que alguns dos blocos tiveram que ser retirados. Vale ressaltar que a pinagem aqui apresentada ainda é para um encapsulamento de 48 pinos, a retirada de novos blocos para que o projeto se encaixe em 40 pinos é uma modificação futura. Todos eles são informados a seguir:

## A.1 ESPELHOS DE CORRENTE NMOS (USO TOTAL: 4 PINOS)

| N° | Tipo/Casamento    | $I_{in}/I_{out}[A]$ | Multiplexação | Observação |

|----|-------------------|---------------------|---------------|------------|

| 1  | Simples/Casado    | 40u/40u             | 0000          |            |

| 2  | Simples/Descasado | 40u/40u             | 0001          |            |

| 3  | Simples/Casado    | 40u/80u             | 0010          |            |

| 4  | Simples/Descasado | 40u/80u             | 0011          |            |

| 5  | Simples/Casado    | 80u/80u             | 0100          |            |

| 6  | Simples/Descasado | 80u/80u             | 0101          |            |

| 7  | Simples/Casado    | 80u/160u            | 0110          |            |

| 8  | Simples/Descasado | 80u/160u            | 0111          |            |

| 9  | Wilson            | 40u/40u             | 1000          |            |

| 10 | Cascode           | 40u/40u             | 1001          |            |

| 11 | Cascode           | 80u/80u             | 1010          |            |

| 12 | Cascode           | 80u/160u            | 1011          |            |

| 13 | Wilson Modificado | 40u/40u             | 1100          |            |

| 14 | Wilson Modificado | 80u/80u             | 1101          |            |

| 15 | High Compliance   | 40u/40u             | 1110          |            |

| 16 | High Compliance   | 80u/80u             | 1111          |            |

Tabela 1: Espelhos de corrente NMOS

# A.2 ESPELHOS DE CORRENTE PMOS(USO TOTAL: 4 PINOS)

| N° | Tipo/Casamento    | $I_{in}/I_{out}[A]$ | Multiplexação | Observação |

|----|-------------------|---------------------|---------------|------------|

| 1  | Simples/Casado    | 40u/40u             | 0000          |            |

| 2  | Simples/Descasado | 40u/40u             | 0001          |            |

| 3  | Simples/Casado    | 40u/80u             | 0010          |            |

| 4  | Simples/Descasado | 40u/80u             | 0011          |            |

| 5  | Simples/Casado    | 80u/80u             | 0100          |            |

| 6  | Simples/Descasado | 80u/80u             | 0101          |            |

| 7  | Simples/Casado    | 80u/160u            | 0110          |            |

| 8  | Simples/Descasado | 80u/160u            | 0111          |            |

| 9  | Wilson            | 40u/40u             | 1000          |            |

| 10 | Cascode           | 40u/40u             | 1001          |            |

| 11 | Cascode           | 80u/80u             | 1010          |            |

| 12 | Cascode           | 80u/160u            | 1011          |            |

| 13 | Wilson Modificado | 40u/40u             | 1100          |            |

| 14 | Wilson Modificado | 80u/80u             | 1101          |            |

| 15 | High Compliance   | 40u/40u             | 1110          |            |

| 16 | High Compliance   | 80u/80u             | 1111          |            |

Tabela 2: Espelhos de corrente PMOS

# A.3 SOMADORES DE CORRENTE BASEADOS EM ESPELHOS CASCODE (USO TOTAL: 3 PINOS)

| N° | Tipo | $I_{in}/I_{out}[A]$ | Pinos | Observação |

|----|------|---------------------|-------|------------|

| 1  | NMOS | 40u/40u/80u         | 3     |            |

| 2  | PMOS | 40u/40u/80u         | 3     | Retirado   |

Tabela 3: Somadores de corrente

# A.4 REFERÊNCIAS DE TENSÃO(USO TOTAL: 0 PINO)

| N° | Descrição                                 |   | Observação |

|----|-------------------------------------------|---|------------|

| 1  | Divisor de tensão NMOS                    | 1 | Retirado   |

| 2  | Divisor de tensão CMOS                    | 1 | Retirado   |

| 3  | Referência de tensão diode connected NMOS | 1 | Retirado   |

| 4  | Referência de tensão diode connected PMOS | 1 | Retirado   |

| 5  | Referência de tensão VBE multiplier       | 1 | Retirado   |

| 6  | Referência de tensão VT multiplier        | 1 | Retirado   |

Tabela 4: Referências de tensão

# A.5 BLOCOS BÁSICOS(USO TOTAL: 25 PINOS)

| N° | Descrição                                                 |   | Observação     |

|----|-----------------------------------------------------------|---|----------------|

| 1  | Amplificador inversor com carga ativa NMOS; $I_B = 40uA$  | 2 |                |

| 2  | Amp. inversor NMOS e Seguidor de fonte NMOS $I_B=20/40uA$ | 3 | BIAS Exclusivo |

| 3  | Amplificador inversor com carga ativa PMOS 40uA           | 2 |                |

| 4  | Seguidor de fonte NMOS; $I_B = 40uA$                      | 2 |                |

| 5  | Seguidor de fonte PMOS; $I_B = 40uA$                      | 2 | Retirado       |

| 6  | Par diferencial NMOS; $I_B = 40uA$                        | 4 |                |

| 7  | Par diferencial PMOS; $I_B = 40uA$                        | 4 |                |

| 8  | Par diferencial PMOS cascode; $I_B = 40uA$                | 4 |                |

| 9  | Bias comum (incluindo polarização do cascode)             | 7 |                |

Tabela 5: Blocos básicos

# A.6 CHAVES ANALÓGICAS(USO TOTAL: 3 PINOS)

| N° | Descrição  | Multiplexação | Observação |

|----|------------|---------------|------------|

| 1  | Chave NMOS | 00            | Retirado   |

| 2  | Chave PMOS | 01            | Retirado   |

| 3  | Chave CMOS | 1             | 1 pino     |

| 4  | Chave CMOS | 1             | 1 pino     |

Tabela 6: Chaves analógicas

# A.7 TRANSISTORES INDEPENDENTES (USO TOTAL: 0 PINO)

| N° | Descrição       | Observação |

|----|-----------------|------------|

| 1  | Transistor NMOS | Retirado   |

| 2  | Transistor PMOS | Retirado   |

Tabela 7: Transistores independentes

# A.8 DECODIFICADOR (USO TOTAL: 5 PINOS)

| N° | Descrição     | Pinos |

|----|---------------|-------|

| 1  | Decodificador | 4     |

| 2  | Enable        | 1     |

Tabela 8: Decodificador

# A.9 ALIMENTAÇÃO EM GERAL (USO TOTAL: 4 PINOS)

| N° | Descrição   | Pinos |

|----|-------------|-------|

| 1  | Alimentação | 4     |

Tabela 9: Alimentação

# APÊNDICE B - CÁLCULO DO TAMANHO DOS TRANSISTORES

Para o cálculo de W/L adota-se a expressão básica para componentes CMOS:

$$I_{REF} = \frac{W}{L} * \frac{1}{2k_x'(V_{GS} - V_t)^2}$$

Onde "x" pode ser substituído por "n" para transistores do tipo NMOS ou "p" para transistores do tipo PMOS.

Sendo:

$$V_{OV} = V_{GS} - V_t$$

Onde  $V_{OV}$  é a tensão de overdrive do transistor, aqui usada com valor  $V_{OV}=200 \mathrm{mV},$  chegamos a:

$$\frac{2*I_{REF}}{k'_{x}*(V_{GS}-V_{t})^{2}} = \frac{W}{L}$$

Para o projeto do Chip usa-se apenas dois valores para correntes de referência (40uA e 80uA), porém trabalha-se com os dois tipos de transistores (NMOS e PMOS), para isso precisa-se dos valores de  $k'_n$  e  $k'_p$ , respectivamente.

Os valores que serão usados  $k_n' = 60 * 10^{-6}$  e  $k_p' = -20 * 10^{-6}$  foram obtidos de uma média de outros projetos com transistores de mesma tecnologia.

Com isso, pode-se montar uma pequena tabela para os valores de referência adotados para o chip:

| $I_{REF}$ | $k'_n$       | $\frac{W}{L}$ |

|-----------|--------------|---------------|

| 40uA      | $60*10^{-6}$ | 34            |

| 80uA      | $60*10^{-6}$ | 66            |

Tabela 10: Tamanho dos transistores NMOS

| $I_{REF}$ | $k_p'$        | $\frac{W}{L}$ |

|-----------|---------------|---------------|

| 40uA      | $-20*10^{-6}$ | 100           |

| 80uA      | $-20*10^{-6}$ | 200           |

Tabela 11: Tamanho dos transistores PMOS